アリオンPCIe電気検証自動化ソリューション (APMS)

APMS(Allion PCIe Multiport System)はアリオン自社開発したPCIe電気検証自動化ソリューションです。 使いやすいUIにより、複雑なPCIe仕様のテストを自動化し、デバイスのキャリブレーションやテストに必要な時間を短縮し、製品開発者に迅速かつ柔軟な方法を提供します。

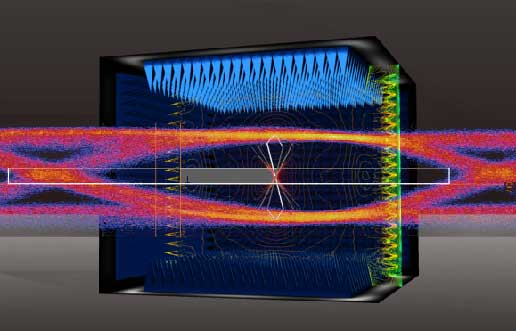

お問い合わせAIと高速演算時代の到来に伴い、高速データ転送ニーズは増加の一途を辿り、PCIe®は特徴の1つが高速伝送をサポートするため、サーバー分野で幅広く使用されます。サーバーの応用エコシステムでは、PCIe®技術の進化に伴い、従来のCEMスロットだけでなく、コンピュータアクセラレータや高速ネットワークカード、高速ストレージデバイスなどの高速伝送製品を接続するためのOCP NIC3.0 や EDSFF E1/E3 Slotへ発展しています。

しかし高速伝送の利便性を楽しむ一方、信号の安全性の問題をもたらします。

このため、PCIeの電気信号測定は、サーバーの品質検証において無視できない重要な項目となっています。

PCIeテストの効率化、お困りですか

すべてのPCIe信号のアイパターンを全面的に検証するには、非常に時間がかかります。たとえば、8つのPCIe 5.0スロット(x16)を持つAIサーバーの場合、測定しなければならないアイパターンは4608個にも及び、作業完了までに9〜10日かかります。

100%測定するには時間がかかるため、業界では検証時間を短縮するために部分的に測定することが多く、その測定カバレッジ率は約15〜25%程度に過ぎません。このような低い測定カバレッジ率では、不適切に設計されたチャネルを検出できないリスクが生じ、データ転送性能の低下や速度低下、深刻な場合にはGPUアクセラレータカードの接続失敗や、システムが再起動する可能性が高まります。

このような背景を考慮し、検証業界で豊富な試験経験とAIソリューションを持つアリオンは、この課題に困るお客様に効果的なソリューションを提供できるよう、測定時間を加速させ、試験サイクルの短縮に貢献するPCIe電気検証自動化ソリューション(APMS)を開発しました。

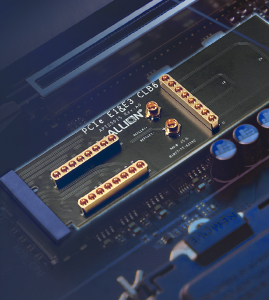

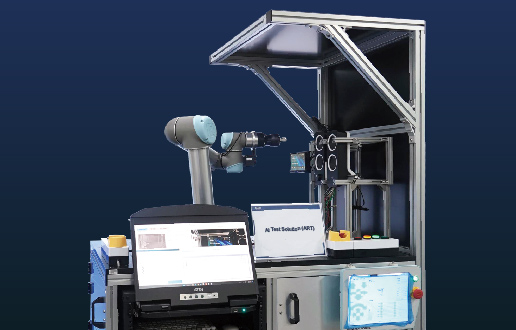

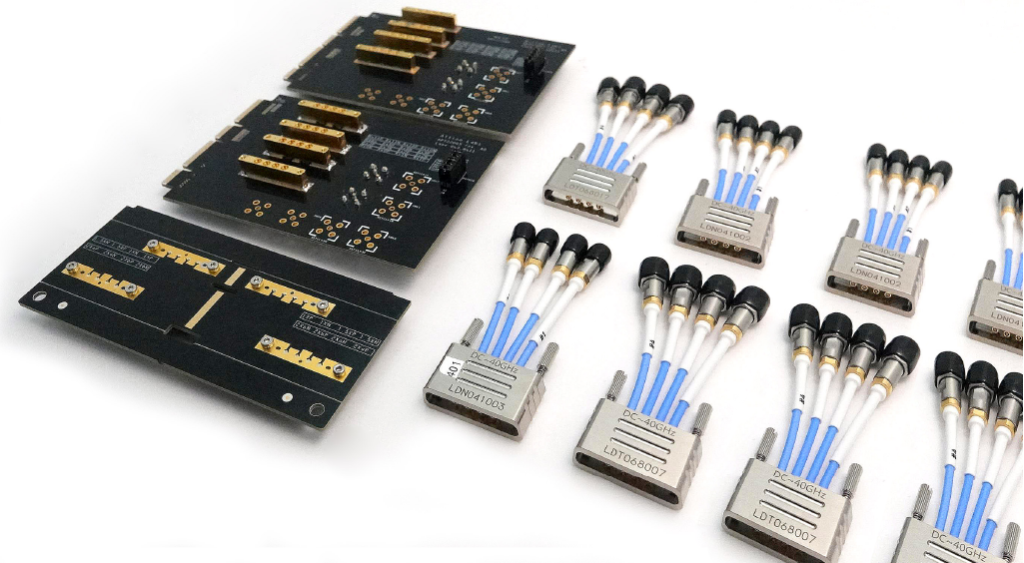

APMSは、スイッチボックス、テストフィクスチャ、ホルダー、自動化ソフトウェアが構成されています。

1) High Speed Lanes Switch

・8レーンの切り替えをサポート

・40GHz に対応

⇒ PCIe 6.0をサポート

・総損失予算が計算される

⇒ 仕様に合わせたS4Pファイルを提供

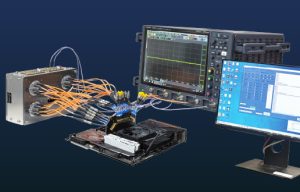

2) Allion Test Fixture

OCP NIC3.0 PCIe CLB5.0 Test Fixture

◆ 主要8レーンは1枚の基板で設計されている

– CEM CLB

» ボート A: L0,3,4,7,8,11,12,15

» ボート B: L1,2,5,6,9,10,13,14

◆ CEMとOCPのCLB5.0は同じ特徴

– ボートAからボートBにCLBを切り替える場合、校正は不要

– CLBをCEMからOCPに切り替えても校正は不要

詳細はもっと見る:OCP NIC3.0 PCIe CLB5.0 Test Fixture

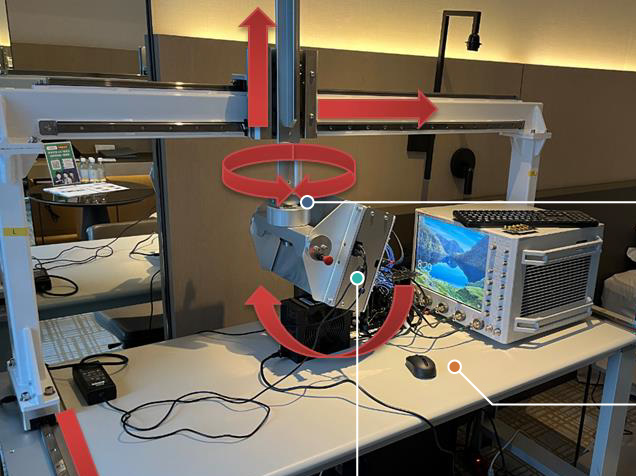

3) Holder Structure

5軸の移動と回転に対応

⇒ X・Y・Zの移動

⇒ 縦の回転: 180 度

⇒ 水平回転: 360 度

4) Automation Control Software

Txテストの場合、ジェネレーション、レーン、プリセットモードなどのオプションがあり、設定ファイルとして保存できます。再テスト時に設定ファイルをロードしていただけるとテストを実行できます。

Sigtestは、マルチスレッド実行により解析時間を短縮し、設定ファイルを自動的に選択し解析の自動化を実現します。またRxテストは、仕様によってマルチレーンのオプションを提供します。

業界初のPCIe SI自動化テストソリューションでテスト時間の短縮に貢献

アリオンは、PCIeテストの複雑性とお客様が直面する課題を考慮し、測定時間をさらに加速する業界初のPCIe自動化テスト・ソリューション(APMS)を開発し、テストサイクルの短縮と設備の利用率を向上させました。このAPMSにより、手動によるテスト時間を5分の1に、従来1カ月かかっていた測定時間を1週間以内に短縮することで、製品開発のスケジュールに大きく貢献します。

【自動化テスト vs. 手動によるテスト】

PCIe Tx テスト時間の比較

| PCIe Test (8 Lanes) |

HW Measurement (Gen1-5, All preset mode) |

SW Conversion |

| Manual Test (Mins) | 240 | 630 |

| APMS (Mins) | 50 | 170 |

| Time Save | 79.17% | 73.02% |

- ハードウェア関連の設定作業の効率

50分以内で完了可能 → 手動によるテストより約79%の時間が短縮可能

- ソフトウェア関連の設定作業の効率

170分以内で完了可能 → 手動によるテストより約73%の時間が短縮可能

PCIe Tx テストレーン数の比較

| PCIe (24 hours ) |

HW Measurement (Gen1-5, All preset mode) (Work time: 8 hours) |

SW Conversion (Off work time: 16 hours ) |

| Manual Test (Lanes) | 16 | None |

| APMS (Lanes) | 76.8 | 45.2 |

- ハードウェア関連

1日だけでテスト完了可能 → 合計約76.8レーン。 手動テストより4.8倍の数を検証可能

- ソフトウェア関連

1日だけでテスト完了可能 → 合計約22.6レーン。 手動テストより3.7倍の数を検証可能