Allion Labs / Tina Yu

はじめに

最近HDMI Forumにて最新版のCTS 2.1c for Sinkが発表されました。このテスト規格の最大のポイントは、FRL Sinkにあります。FRL (Fixed Rate Link)伝送技術はHDMI 2.1データ伝送で用いられており、8K映像でも使われています。その特徴は以下の通りです。

- FRLはFixed Rate Linkの略称で、その名の通り固定比率帯域幅のことである。

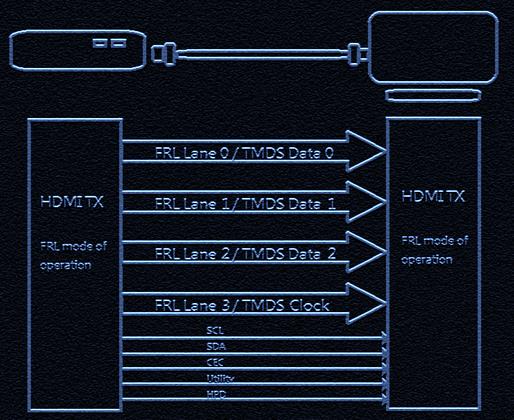

- 従来のTMDS クロック、Data 0、Data 1、Data 2がそれぞれFRL Lane 0、Lane 1、Lane 2、Lane 3に対応している。

- DPのEmbedded CKモードの様に、専用のクロックチャンネルを必要としないため、AV信号がLane 3だけでなくLane 4でも伝送可能である。

- エンコード方式が8b/10bを16b/18bへと変わり、エンコード効率が9%改善されている。

- VESAのDSC圧縮技術を採用し、解像度は10K@120に達する。

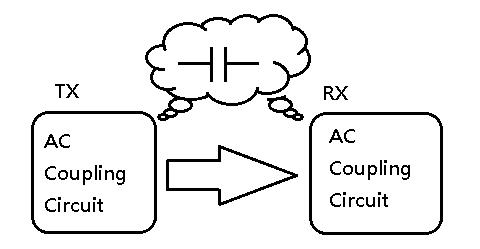

- DC-coupled TMDSの伝送方式と違い、AC-coupled FRLの伝送方式へと変更されている。

- FRL Link Trainingの通信により、TMDSモードと後方互換性がある。

FRL伝送規格の説明

ではFRLの規格についてお話します。FRLはFixed Rate Linkの略称で、固定データ量が解像度の大きさによって右されない伝送技術のことを指します。FRLモード操作において、同時に3または4つのLaneでデータ伝送が可能です。3 LaneモードではLane 3が閉じられ、4 LaneモードではどのLaneでも12Gbpsによる伝送が可能です。FRL Lane link ratesについては、下の表1をご参照ください。

表1:FRL Lane link rates

| Number of Lanes | Rate per Lane | Total Bandwidth |

| 3 | 3 Gbps | 9 Gbps |

| 3 | 6 Gbps | 12 Gbps |

| 4 | 6 Gbps | 24 Gbps |

| 4 | 8 Gbps | 32 Gbps |

| 4 | 10 Gbps | 40 Gbps |

| 4 | 12 Gbps | 48 Gbps |

FRLをどのように実現するか (電気編)

TMDSモードのHDMI Sourceは、DC couplingしかサポートしませんが、FRLモードのHDMI Sourceは、AC couplingにも対応しているため、HDMI 2.1の規格書にある通り、AC Coupling Capacitor(100nF to 250nF)に定義されています。この規定に基づき、AC common Mode Noiseもこの規格書に規定されており、HDMI SinkはHDMI 1.4の時、DC coupledとAC coupledをサポートすると規定されています。

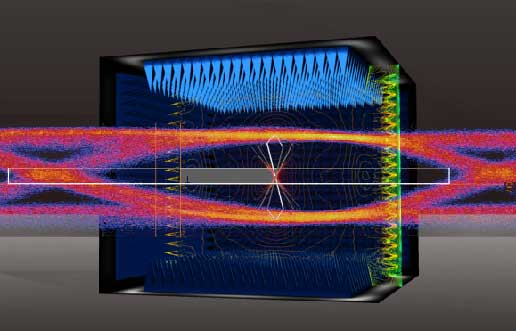

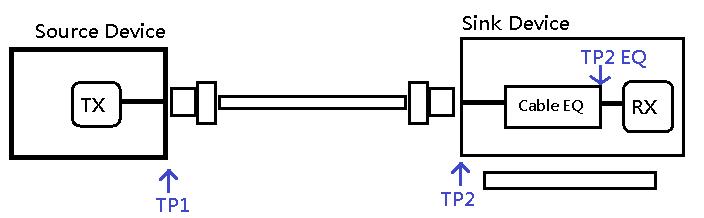

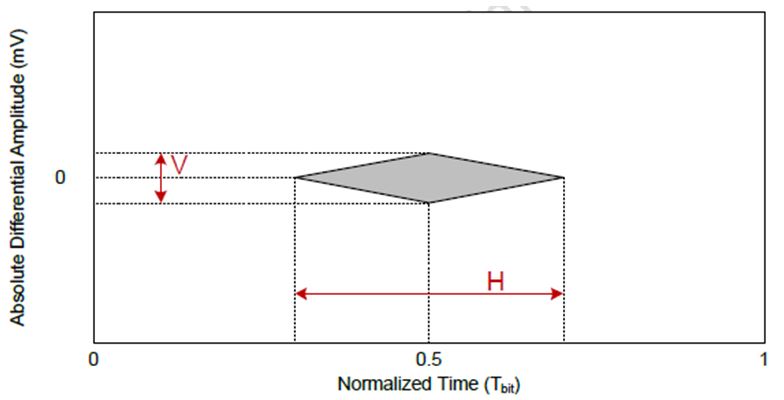

アイパターンに関しては、この規格書でもTP1アイパターンへの言及はなく、TP2 EQアイパターンの規定について触れられています。一番の違いは、そのクロック信号のジッター特性がFRLモードを含まないことです。これに取って代わったのは、random jitterとdeterministic jitterを含むジッターです。

以下のHDMI 2.1規格におけるTP2 EQアイパターンをご参照ください。

| FRL Bit Rate | H | V |

| 3 Gbps | 0.5 | 150 |

| 6 Gbps | 0.4 | 150 |

| 8 Gbps | 0.385 | 135 |

| 10 Gbps | 0.37 | 120 |

| 12 Gbps | 0.35 | 100 |

表2:帯域幅によるマスク仕様

FRLをどのように実現するか (プロトコル編)

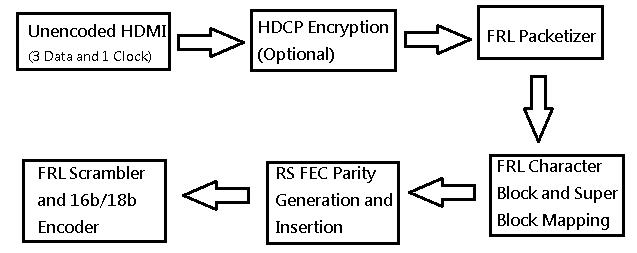

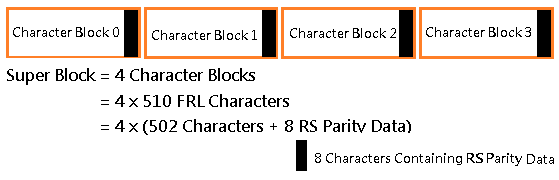

FRLはTMDSと後方互換性があるため、下の図5にてメインプロトコルレイヤーの規定をご参照ください。まず、3本のデータ送信用チャンネルと1本のクロック信号送信用無圧縮映像チャンネルに加え、HDCP暗号化が組み込まれた後に適用の有無を選ぶことができます。その直後、FRLパケット化が502のFRL文字コードを形成し、どの文字コードブロックも後に8つの文字コードRS FEC parityデータがあるため、合計で510のFRL文字コードブロックを形成しまた4つのFRL文字コードブロックで1つのスーパーブロックを形成します。

FRLをどのように実現するか (コントロール編)

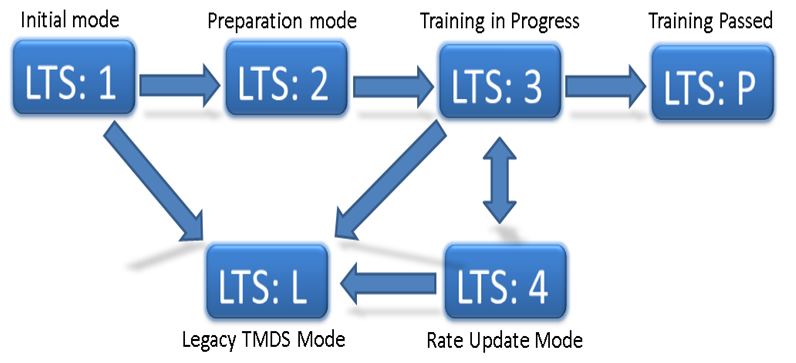

TMDSモードとFRLモードの間の切り換えはFRL Link Trainingに依存しており、これも重要な通信技術の一つです。最初の接続あるいは別のFRLデータモードに切り換える際、FRL Link Trainingが用いられます。下の図7は、各Link Trainingの状態を表したものです。合計で6つの状態があります。

- LTS1はSourceが SinkのEDIDを読み取った内容。

- LTS2はSourceとSinkのFRLが準備している状態。

- LTS3において、SinkはLink Training Pattern及びUpdate flagを通じて、特定のFRL RateのSourceと通信を行う。

- LTS4は、別のFRL rateに切り換える際に用いられ、最後にLTSPが表示されLink Trainingが完了すると、FRL伝送が始まる

LTSLはFRL Link Trainingの通信失敗であり、その後TMDSモードが起動します。

TMDSは取って代わられるか

HDMI 2.1インターフェイスピンの割り当ては、従来バージョンとの間に差異はありませんが、HDMI 2.1の8K規格とHDMI 2.0の4K規格は別々の技術によって達成されたものです。あるレベルでは、FRLも従来のバージョンに比べ、より厳密で複雑なものになっています。よって従来のHDMI 1.4/2.0に対応するため、HDMI 2.1 specificationはFRLをサポートするHDMI製品は、TMDSもサポートしなければならないと規定されています。この規定はHDMI 2.1規定をクリアした製品が、マーケットにある他の製品と相互接続性を持つことを確保し、旧来のHDMI 1.4/2.0の規格をクリアした製品に対する相互接続性問題の発生を防止しています。

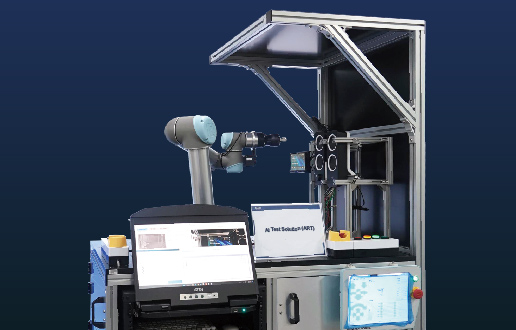

アリオンのHDMI 2.1テスト案

8KテレビのメーカーがHDMI 2.1認証をすぐに取得できるように、アリオンは以下の完全なテスト案をご用意しています。もしご不明な点ございましたら、アリオンのお問い合わせフォームよりお気軽にご連絡ください。

- HDMI 2.1認証テスト

- TMDSモード

- TMDS Electrical Test

- TMDS Protocol Test

- Pixel Decoding Test

- Video Timing Test

- EDID Test

- E-DDC Test

- FRLモード

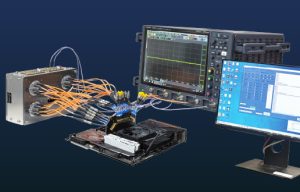

- FRL Electrical Test

- FRL Protocol Test

- FRL Pixel Decoding Test

- FRL Video Timing Test

- FRL E-EDID Test

- TMDSモード

- HDMI 1.4認証テスト

- EDID/E-DDC Test

- Electrical Test

- Protocol Test

- Video Test

- Audio Test1325

- Interoperability with DVI Test

- Advanced Features